Electrostatic Discharge (ESD) Simulation and Prediction for RF Devices

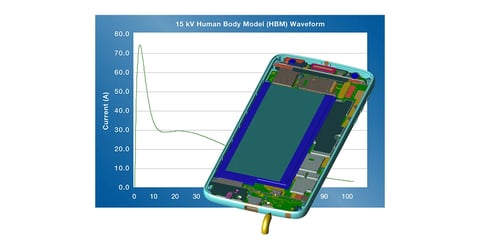

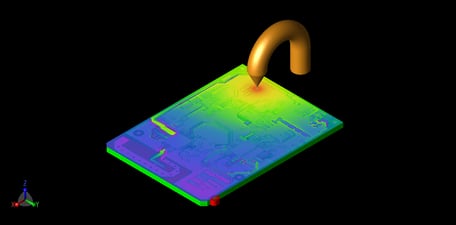

Electrostatic discharge (ESD) testing is utilized worldwide by electronics manufactures and includes the use of numerous standards from organizations including the American National Standards Institute (ANSI), JEDEC, and International Electrotechnical Commission (IEC), among others. ESD testing requires the use of many hardware prototypes, which is time consuming and expensive. The ability to simulate the ESD testing process and pinpoint locations in wireless devices susceptible to ESD damage would be extremely valuable and allow engineers to reduce the number of prototypes required to design products for minimal ESD damage.

Electrostatic discharge (ESD) testing is utilized worldwide by electronics manufactures and includes the use of numerous standards from organizations including the American National Standards Institute (ANSI), JEDEC, and International Electrotechnical Commission (IEC), among others. ESD testing requires the use of many hardware prototypes, which is time consuming and expensive. The ability to simulate the ESD testing process and pinpoint locations in wireless devices susceptible to ESD damage would be extremely valuable and allow engineers to reduce the number of prototypes required to design products for minimal ESD damage.

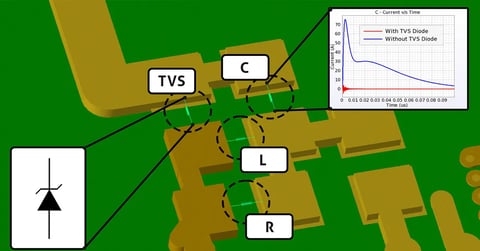

This presentation demonstrates a new multiphysics-based ESD analysis capability which allows the ESD testing process to be analyzed via computer simulation. This will save companies time and money by allowing ESD protection to be optimized during the design phase, thus reducing the number of prototypes required to be built and tested.